## **Integrated Passives**

Carsten Wulff, carsten@wulff.no

#### I. METAL IN ICS IS NOT WIRE IN SCHEMATIC

Metal wires in an integrated circuit comes in two types, copper and aluminium.

Most of the routing layers will be copper. To ensure that the copper ions don't diffuse into the silicon-oxide a barrier material surrounds all copper interconnect.

Copper is too stiff to be wire-bonded. As such, the top layer metals would be aluminium.

Since the routing is so small, we have to care about the parasitic properties of the routing. Below is a table with some common quantities for copper. For example, if we have 1000  $\mu m$  metal wire with 1  $\mu m$  width, then it would be approximately 150  $\Omega,$  1 nH , 1 pF and tolerate a maximum of 1 mA DC current.

| Parameter      | Typ. Value | Unit           |

|----------------|------------|----------------|

| Resistance     | 150        | $m\Omega/\Box$ |

| Capacitance    | 1          | $fF/\mu m$     |

| Inductance     | 1          | nH/mm          |

| Max DC current | 1          | mA/□           |

The type of circuit we have determine what we must simulate. Everything needs to be simulated with parasite capacitance and max current. Only RF, however, usually needs to be simulated with resistance, capacitance, inductance and maximum current.

| Circuit type        | Must simulate/know |

|---------------------|--------------------|

| All                 | C Imax             |

| Analog, Power       | R C Imax           |

| Some RF, Some Power | R L C Imax         |

To simulate the effects of parasitics, we need a description of the technology. A Process Design Kit (PDK). Most PDKs are closely guarded secrets, as they describe many things about the way the foundry makes the integrated circuits.

Some PDKs are open source, however, see Skywater 130 nm and IHP-Open-PDK

In addition to the PDK, we need tools that can calculate from the layout the parasitic elements. Some of the tools are

Layout parasitic extraction tools

- Calibre xRC

- Synopsys StarRC

- Cadence Quantus

- Magic VLSI

3D EM Simulators

- Keysight ADS

- HFSS

Transistor CAD (TCAD)

• Synopsys TCAD

#### II. RESISTORS

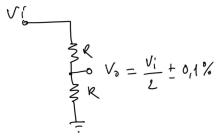

Sometimes we want a specific resistance. In general, any resistance on IC will vary in absolute value by maybe up to  $\pm$  20 %. The relative size, however, can be controlled to within 0.1 %.

In other words, you can't rely on a 1 kOhm resistor actually being 1 kOhm, it might be 0.8 kOhm. If you have two, however, you can trust that both of them will be 0.8 kOhm.

That's why almost all analog circuits rely on the relative sizes of passives, not the absolute value. If a circuit does rely on absolute values, then it usually needs to be trimmed in production.

#### A. Polysilicon

Can be both N-doped, and P-doped

Often with two flavors, with, and without silicide

Silicide reduces resistance of polysilicon

#### B. Diffusion

Use doped region as resistor

Usually without silicide

Non-linear capacitance

Tricky temperature dependence

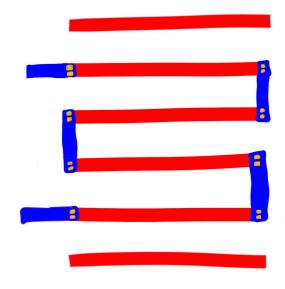

#### C. Metal

Usually too low omhic to be a useful resistor

Useful for "separating nets" in schematic and layout

Must be considered for power supply and ground routing (high currents)

#### III. CAPACITORS

# A. What is S, M, L, XL on a chip? nRF52832

$3200\mu m \times 3000\mu m = 9600k\mu m^2$

S

$< 5 \ k\mu m^2$

M

$< 50 \ k \mu m^2$

L

$< 200 \ k\mu m^2$

XL

$> 200 \ k\mu m^2$

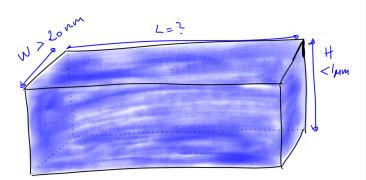

# B. Metal-Oxide-Metal finger capacitors Unit capacitance

$$\approx 1 fF/\mu m^2/layer$$

$$10pF = 100\mu m \times 100\mu m = 10k\mu m^2$$

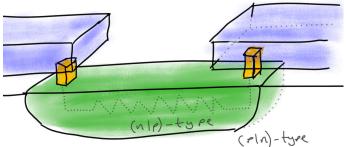

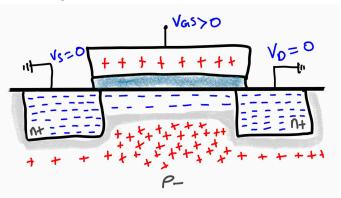

#### C. MOS capacitors

dicex/sim/spice/NCHIO/vcap.cir

\* gate cap

.include ../../models/ptm\_130.spi

vdrain D 0 dc 1 vgaini G 0 dc 0.5 vbulk B 0 dc 0 vcur S 0 dc 0

M1 D G S B nmos w=1u l=1u

.op

#### Moscap is

$\approx 10 fF/\mu m^2$

#### $10pF = 31\mu m \times 31\mu m \approx 1k\mu m^2$

dicex/sim/spice/NCHIO/vcap.vlog

Device m1:

Vgs (gate-source voltage) [V] : 0.5 Vgd (gate-drain voltage) [V] : -0.5Vds (drain-source voltage) : 1 [V] : 1.90808e-12 Vbs (bulk-source voltage) Vbd (bulk-drain voltage) [A] : 7.32634e-06 Ιd (drain current)

(source current) Ιs [A] -7.32633e-06 (bulk-drain current) -1.01e-12 Ibs (bulk-source current) [A] : 9.581e-25 Vt (threshold voltage) [V] : 0.378198 [V] : 0.121802 Vqt (gate overdrive voltage) Vgsteff [V] : 0.12515 (effective vgt) (transconductance) [S] : 8.44164e-05 Gm [S]: 2.00071e-05 (bulk bias transconductance)

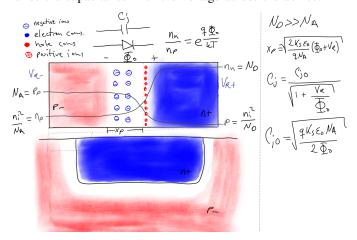

#### D. Varactors

A variator is a "variable capacitor", usually it's a device that varies the capacitance with the voltage across the device.

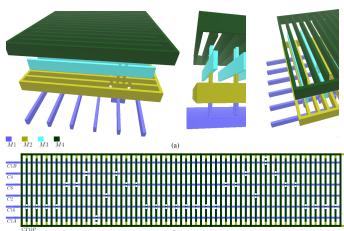

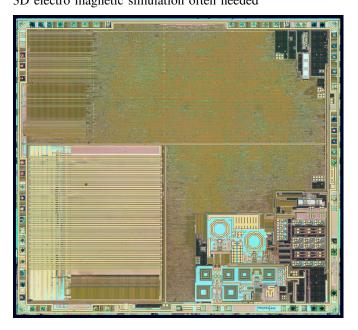

#### IV. INDUCTORS

Usually two top metals, because they are thick (low ohmic)

3D electro magnetic simulation often needed

Use foundry model

### V. VARIATION IN PASSIVES

Absolute value for resistors and capacitors

$$\approx \pm 10$$

% to

$\pm 20$

%

Relative precision for closely spaced devices

$\approx$

0.1 % to 1 %

Relative precision for devices on same die

> 2

% or more

#### VI. RELATIVE PRECISION

Resistors and Capacitors can be matched extremely well

$$\begin{array}{ccc}

\sqrt{1} & \sqrt{2} & Q_1 = CV_1 \\

& & \boxed{1} & Q_2 = CV_2 \\

& & \boxed{Q_1} & = \frac{V_1}{V_2} & = 0.1\%

\end{array}$$

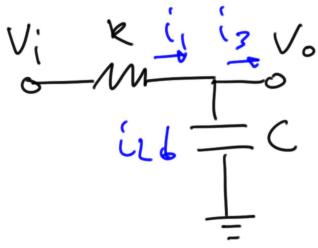

$$i_3 = 0 = i_1 - i_2$$

$$0 = \frac{V_i - V_o}{R} - \frac{V_o}{1/sC}$$

$$0 = V_i - V_o - V_o sRC$$

$$V_o(1 + sRC) = V_i$$

$$\frac{V_o}{V_i} = \frac{1}{1 + sRC}$$

Assume standard deviation (

$\sigma$

$)^1$  of

$$\sigma_R = 20$$

%.

$$\sigma_C = 20$$

%

$$\sigma_{RC} = \sqrt{0.2^2 + 0.2^2} = 28$$

%

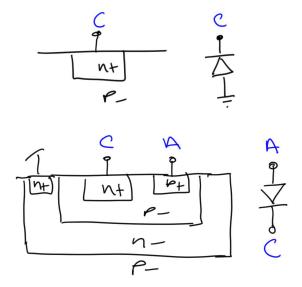

### VII. DIODES

#### Many, many ways

Reverse bias diodes to ground are useful for signals with long routing to transistor gate. Protects gate from breakdown during chemical mechanical polish.

<sup>&</sup>lt;sup>1</sup>If you don't remember how standard deviation works, read Introduction to mathematics of noise sources

Carsten Wulff received the M.Sc. and Ph.D. degrees in electrical engineering from the Department of Electronics and Telecommunication, Norwegian University of Science and Technology (NTNU), in 2002 and 2008, respectively. During his Ph.D. work at NTNU, he worked on open-loop sigma-

delta modulators and analog-to-digital converters in nanoscale CMOS technologies. In 2006-2007, he was a Visiting Researcher with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON, Canada. Since 2008 he's been with Nordic Semiconductor in various roles, from analog designer, to Wireless Group Manager, to currently Principle IC Scientist. He's also an Adjunct Associate Professor at NTNU. His present research interests includes analog and mixed-signal CMOS design, design of high-efficiency analog-to-digital converters and low-power wireless transceivers. He is the developer of Custom IC Compiler, a general purpose integrated circuit compiler.