*Lecture Notes* 2025

CARSTEN WULFF

Built on Sun Jun 22 14:18:38 UTC 2025 from 37bf2cd8ff6cd72ae7b7d46a6ffd4a790fa71425 © Carsten Wulff 2025

## **Contents**

| C | onten | ts                                                 | 3  |

|---|-------|----------------------------------------------------|----|

| 1 | Back  | kground                                            | 1  |

| 2 | Intro | oduction                                           | 3  |

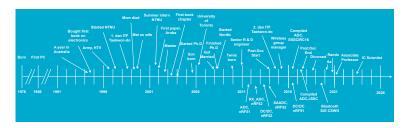

|   | 2.1   | Who                                                | 3  |

|   | 2.2   | How I see our roles                                | 3  |

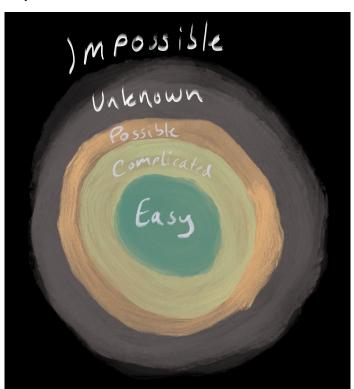

|   | 2.3   | I want you to learn the skills necessary to make   |    |

|   |       | your own ICs                                       | 4  |

|   | 2.4   | There will always be analog circuits, because the  |    |

|   |       | real world is analog                               | 5  |

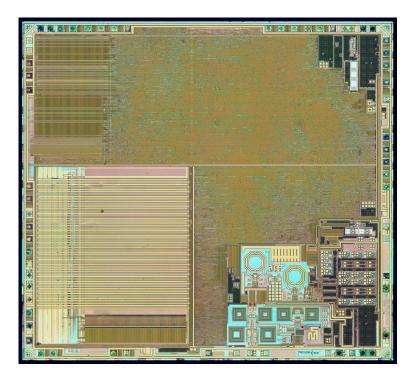

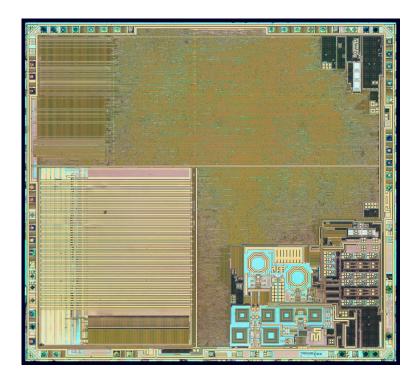

|   | 2.5   | Will you tape-out an IC?                           | 6  |

|   |       | 2.5.1 What the team needs to know to design ICs    | 6  |

|   |       | 2.5.2 Zen of IC design (stolen from Zen of Python) | 7  |

|   |       | 2.5.3 IC design mantra                             | 7  |

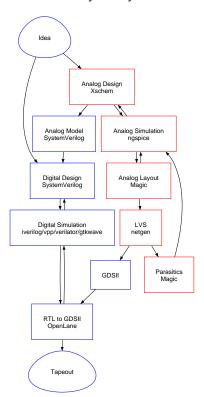

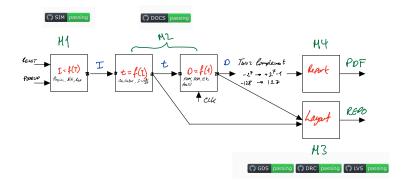

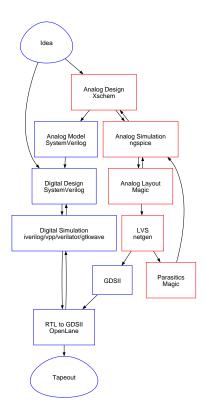

|   |       | 2.5.4 Analog Design Process                        | 8  |

|   | 2.6   | My Goal                                            | 8  |

|   | 2.7   | Syllabus                                           | 9  |

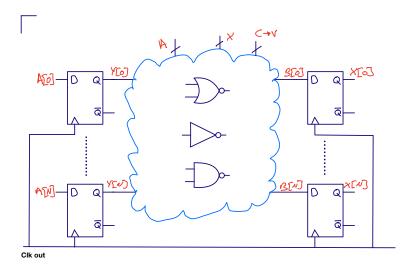

|   | 2.8   | Project JNW (2025)                                 | 9  |

|   |       | 2.8.1 Grading                                      | 11 |

|   | • •   | 2.8.2 Group dynamics                               | 11 |

|   | 2.9   | Software                                           | 12 |

| 3 | A Re  | efresher                                           | 13 |

|   | 3.1   | There are standard units of measurement            | 13 |

|   | 3.2   | Electrons                                          | 14 |

|   | 3.3   | Probability                                        | 15 |

|   | 3.4   | Uncertainty principle                              | 15 |

|   | 3.5   | States as a function of time and space             | 15 |

|   | 3.6   | Allowed energy levels in atoms                     | 16 |

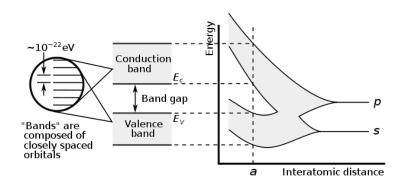

|   | 3.7   | Allowed energy levels in solids                    | 16 |

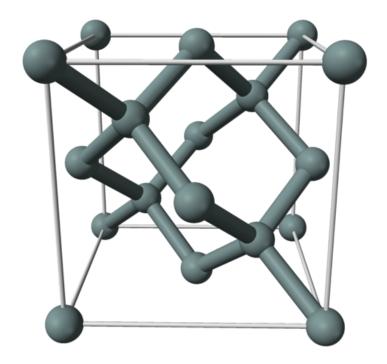

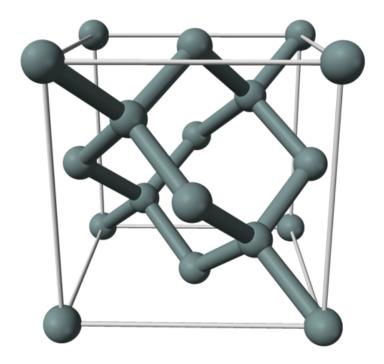

|   | 3.8   | Silicon Unit Cell                                  | 17 |

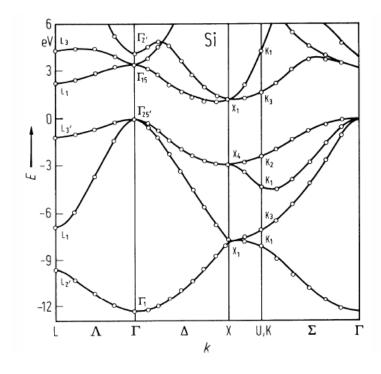

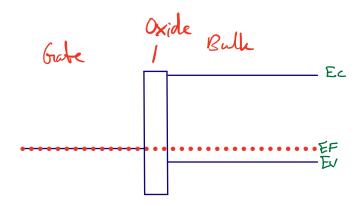

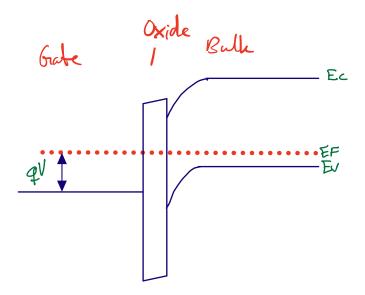

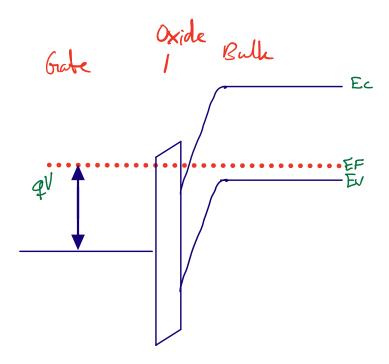

|   | 3.9   | Band structure                                     | 18 |

|   | 3.10  | Valence band and Conduction band                   | 19 |

|   | 3.11  | Fermi level                                        | 19 |

|   | 3.12  | Metals                                             | 20 |

|   | 3.13  | Insulators                                         | 20 |

|   | 3.14  | Semiconductors                                     | 21 |

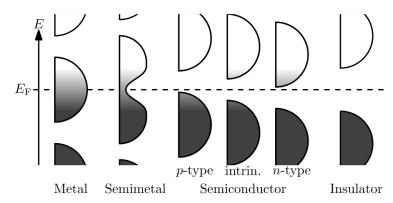

|   | 3.15  | Band diagrams                                      | 21 |

|   | 3.16  | Density of electrons/holes                         | 21 |

|   | 3.17  | Fields                                             | 22 |

|   | 3.18  | Permittivity and Permeability                      | 22 |

|   | 3.19  | Quantum electrodynamics                            | 23 |

|   | 3.20  | O                                                  | 23 |

|   | 3.21  | Current                                            | 23 |

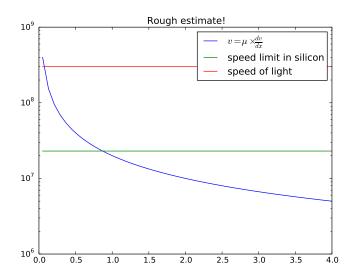

|   | 3.22  |                                                    | 24 |

|   | 3 23  | Diffusion current                                  | 25 |

|   | 3.24 | Why a            | re there two currents?                   | 25              |

|---|------|------------------|------------------------------------------|-----------------|

|   | 3.25 | Curre            | nts in a semiconductor                   | 25              |

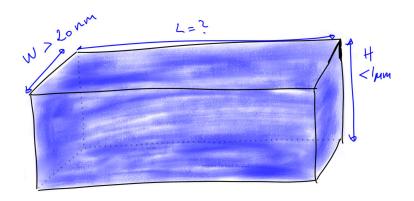

|   | 3.26 | Resisto          | ors                                      | 26              |

|   | 3.27 |                  | itors                                    | 26              |

|   | 3.28 | Induct           | tors                                     | 26              |

|   |      | _                |                                          |                 |

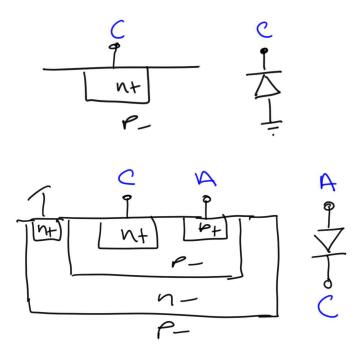

| 4 | Dio  |                  |                                          | 27              |

|   | 4.1  | -                |                                          | 27              |

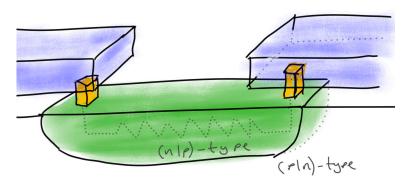

|   | 4.2  |                  | 1                                        | 27              |

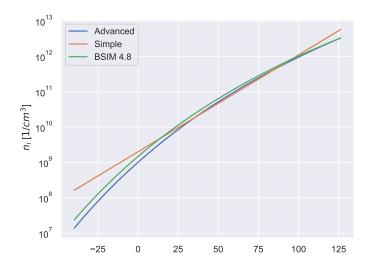

|   | 4.3  |                  | sic carrier concentration                | 29              |

|   | 4.4  |                  | quantum                                  | 30              |

|   |      | 4.4.1            | Density of states                        | 32              |

|   |      | 4.4.2            | How to think about electrons (and holes) | 34              |

|   | 4.5  | -                | g                                        | 35              |

|   | 4.6  |                  | nctions                                  | 36              |

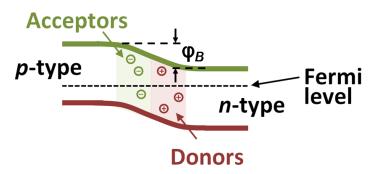

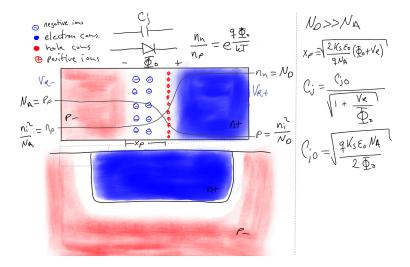

|   |      | 4.6.1            | Built-in voltage                         | 36              |

|   |      | 4.6.2            | Current                                  | 37              |

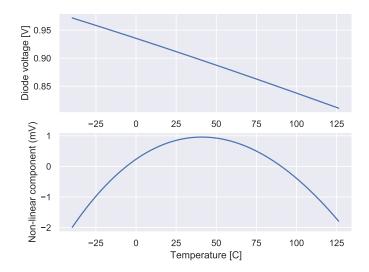

|   |      | 4.6.3            | Forward voltage temperature dependence   | 39              |

|   |      | 4.6.4            | Current proportional to temperature      | 40              |

|   | 4.7  | -                | ions aren't real                         | 41              |

|   |      | Referen          | nces                                     | 42              |

| 5 | Nois | 20               |                                          | 43              |

| 3 | 5.1  |                  |                                          | 43              |

|   | 5.2  |                  |                                          | 43              |

|   | 5.2  |                  | ics                                      | $\frac{43}{44}$ |

|   | 5.4  |                  | ge Power                                 | 45              |

|   | 5.5  |                  | Spectrum                                 | 46              |

|   | 5.6  |                  | bility Distribution                      | 47              |

|   | 5.7  |                  |                                          | 47              |

|   | 5.8  |                  | to Noise Ratios                          | 48              |

|   | 5.9  | _                | figure and Friis formula                 | 49              |

|   | 5.10 |                  | e                                        | 49              |

|   | 5.10 | _                | al Density                               | 50              |

|   |      | 5.10.1<br>5.10.2 | Sources of Confusion                     |                 |

|   |      |                  |                                          | 50              |

|   |      | 5.10.3<br>5.10.4 | Example: Thermal Noise                   | 52<br>52        |

|   |      | 5.10.4           | Einstein: The source                     | 52              |

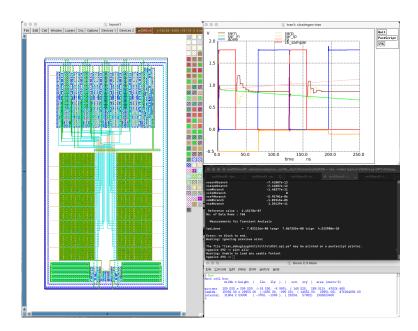

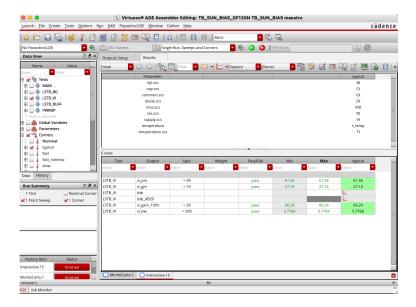

| 6 | Sky  | 130nm t          | utorial                                  | 55              |

|   | 6.1  | Tools            |                                          | 55              |

|   |      | 6.1.1            | Setup WSL (Applicable for Windows users) | 55              |

|   |      | 6.1.2            | Setup public key towards github          | 55              |

|   |      | 6.1.3            | Provide git with author identity         | 56              |

|   |      | 6.1.4            | Get AICEX and setup your shell           | 56              |

|   |      | 6.1.5            | On systems with python $3 > 3.12 \dots$  | 56              |

|   |      | 6.1.6            | Install Tools                            | 57              |

|   |      | 6.1.7            | Install cicconf                          | 57              |

|   |      | 6.1.8            | Install cicsim                           | 58              |

|   |      | 6.1.9            | Setup your ngspice settings              | 58              |

|   | 6.2  |                  | that magic and xschem works              | 58              |

|   |      | 222001           | 0                                        | - 0             |

|   | 6.3        | Desig   | n tutorial                                   | 58       |

|---|------------|---------|----------------------------------------------|----------|

|   |            | 6.3.1   | Create the IP                                | 58       |

|   |            | 6.3.2   | The file structure                           | 58       |

|   |            | 6.3.3   | Github setup                                 | 60       |

|   |            | 6.3.4   | Start working                                | 61       |

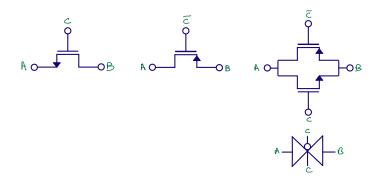

|   |            | 6.3.5   | Draw Schematic                               | 61       |

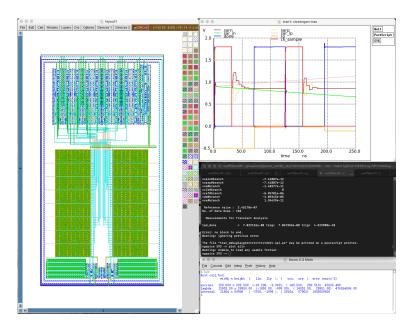

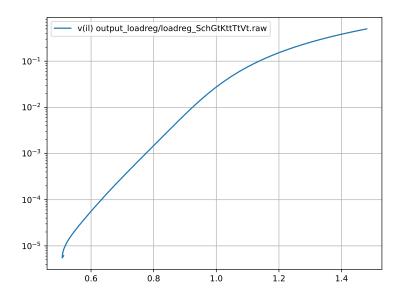

|   |            | 6.3.6   | Typical corner SPICE simulation              | 62       |

|   |            | 6.3.7   | All corners SPICE simulations                | 65       |

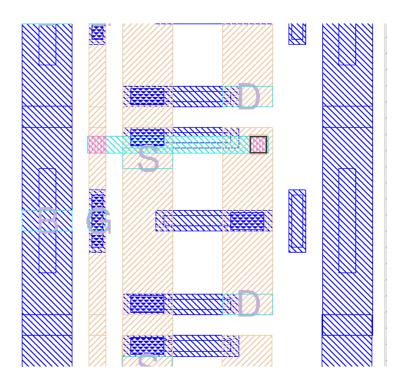

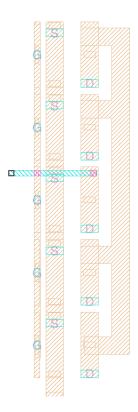

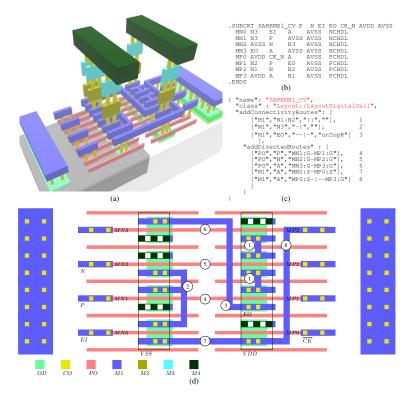

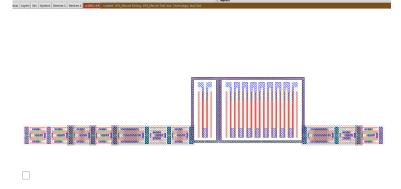

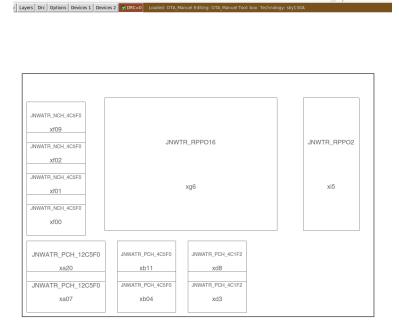

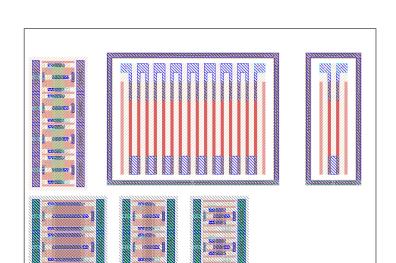

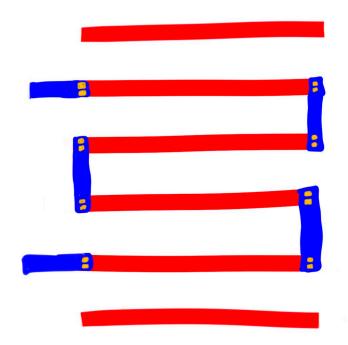

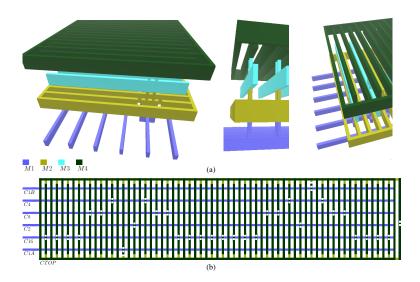

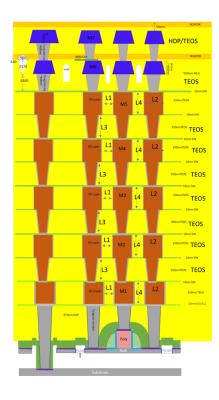

|   |            | 6.3.8   | Draw Layout                                  | 67       |

|   |            | 6.3.9   | Layout verification                          | 72       |

|   |            | 6.3.10  | Extract layout parasitics                    | 72       |

|   |            | 6.3.11  | Simulate with layout parasitics              | 73       |

|   |            | 6.3.12  | Make documentation                           | 73       |

|   |            | 6.3.13  | Edit info.yaml                               | 74       |

|   |            | 6.3.14  | Setup github pages                           | 74       |

|   |            | 6.3.15  | Frequency asked questions                    | 74       |

|   |            |         | 1 / 1                                        |          |

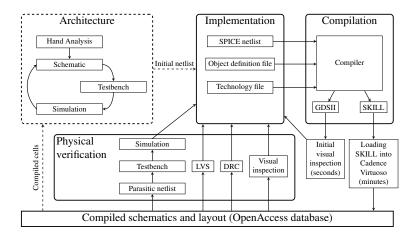

| 7 | Ana        | log Des |                                              | 75       |

|   | 7.1        |         | dist                                         | 75       |

|   |            | 7.1.1   | Specification                                | 75       |

|   |            | 7.1.2   | Design                                       | 76       |

|   |            | 7.1.3   | Tapeout                                      | 76       |

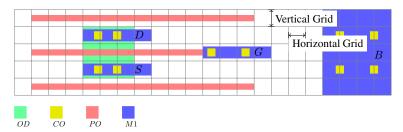

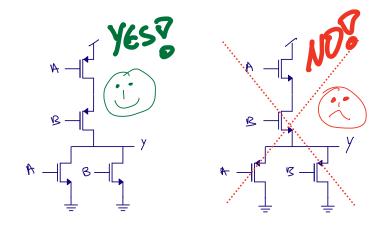

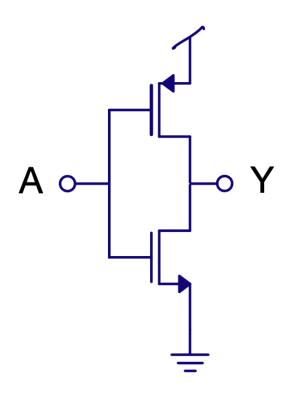

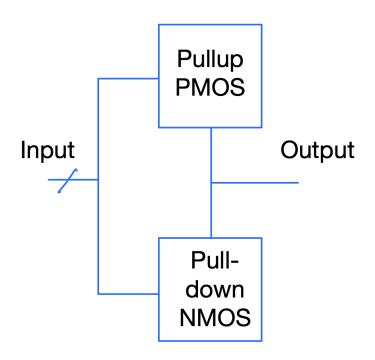

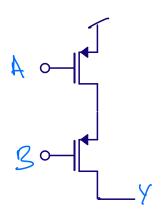

|   | 7.2        |         | natic rules                                  | 76       |

|   | 7.3        | Layou   | ıt rules                                     | 78       |

| 0 | IC a       | 4 ECD   |                                              | 01       |

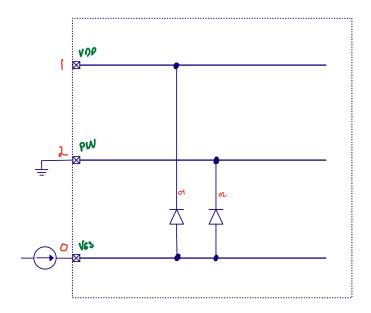

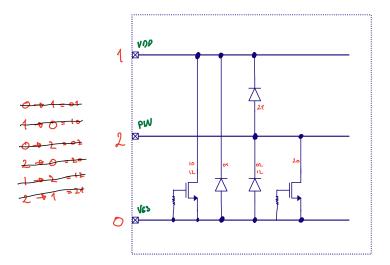

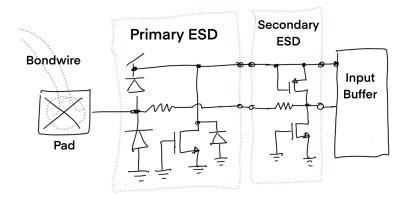

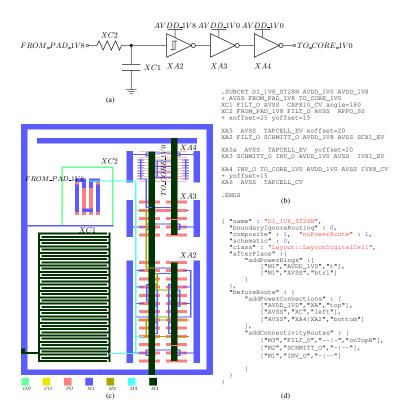

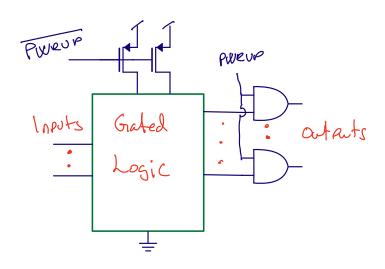

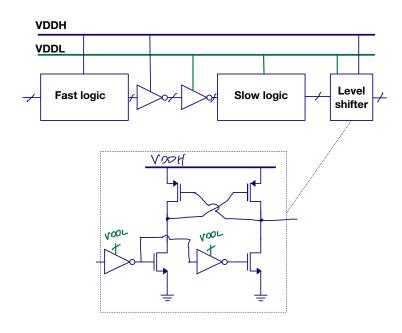

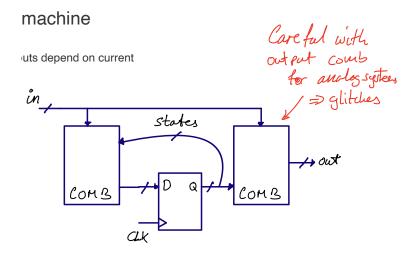

| 8 |            | nd ESD  | blocks must our IC include?                  | 81       |

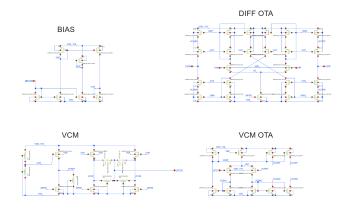

|   | 8.1<br>8.2 |         |                                              | 81<br>84 |

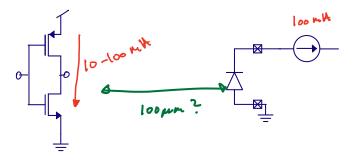

|   | 0.2        |         | ostatic Discharge                            |          |

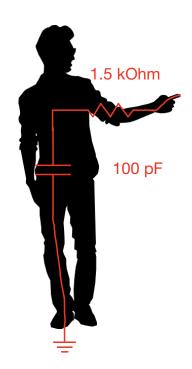

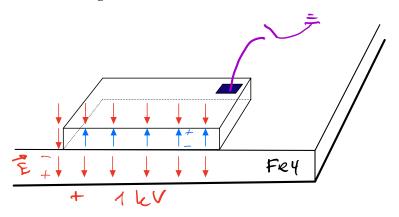

|   |            | 8.2.1   | Human body model (HBM)                       | 86       |

|   | 0.2        | 8.2.2   | Charged device model (CDM)                   | 86       |

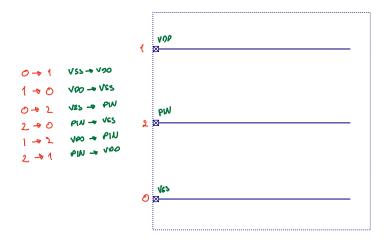

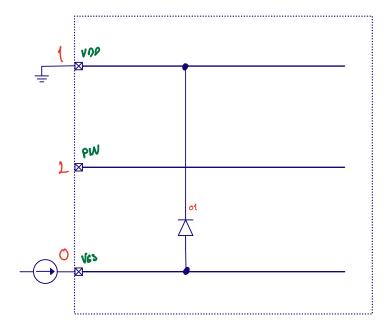

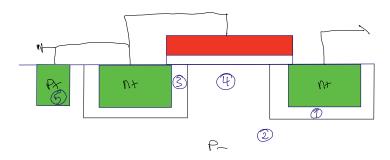

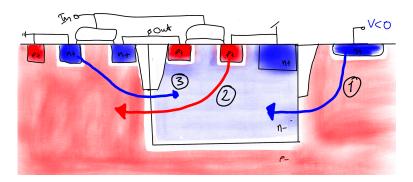

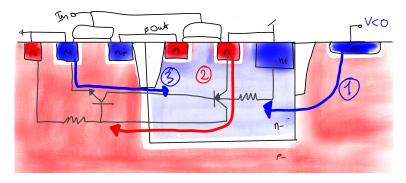

|   | 8.3        |         | BM ESD zap example                           | 88       |

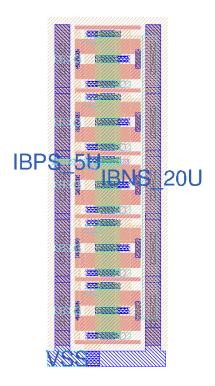

|   | 8.4        |         | rounded gate NMOS                            | 91       |

|   | 8.5        |         | just want a digital input, what do I need? . | 94       |

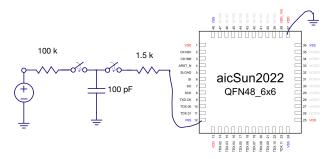

|   | 0.6        | 8.5.1   | Input buffer                                 | 95       |

|   | 8.6        |         | -up                                          | 96       |

|   | 8.7        | vvant   | to learn more?                               | 99       |

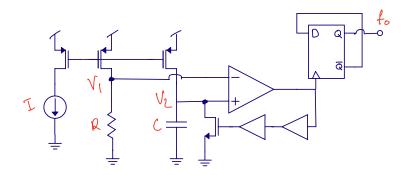

| 9 | Refe       | erences | and bias                                     | 101      |

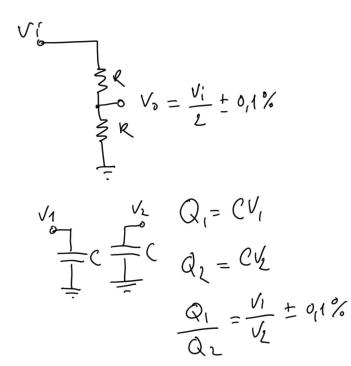

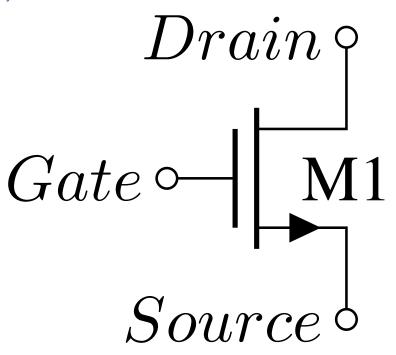

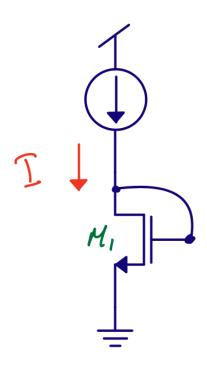

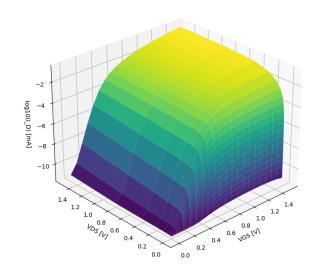

|   | 9.1        |         | ng                                           | 101      |

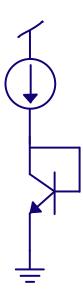

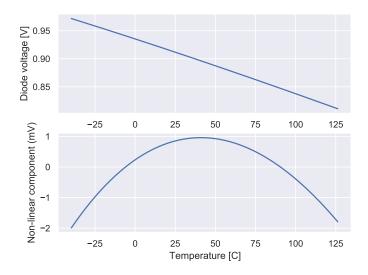

|   | 9.2        |         | gap voltage reference                        | 104      |

|   |            | 9.2.1   | A voltage complementary to temperature       |          |

|   |            |         | (CTAT)                                       | 104      |

|   |            | 9.2.2   | A current proportional to temperature        |          |

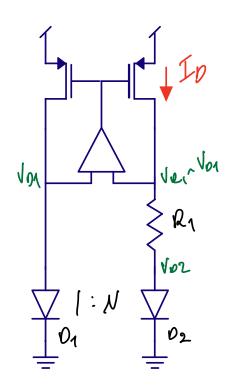

|   |            |         | (PTAT)                                       | 105      |

|   |            | 9.2.3   | How to combine a CTAT with a PTAT? .         | 106      |

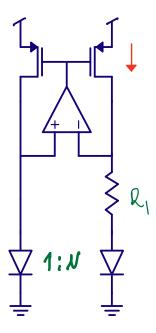

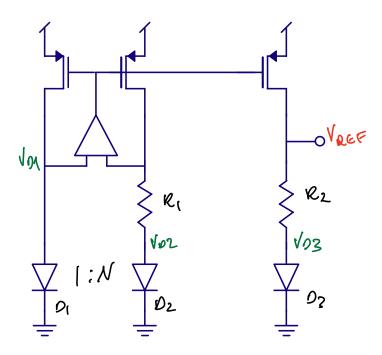

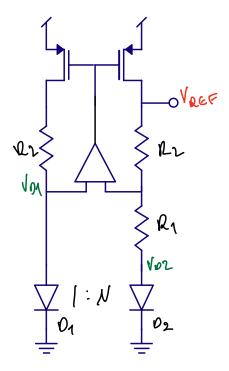

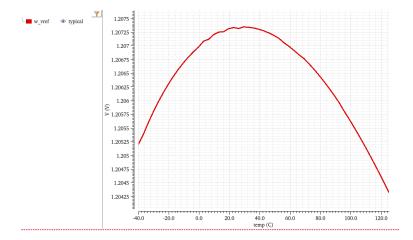

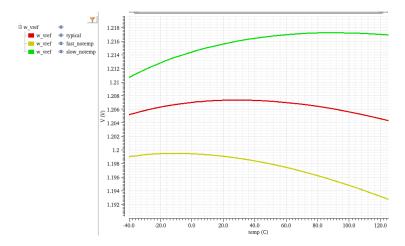

|   |            | 9.2.4   | Brokaw reference                             | 107      |

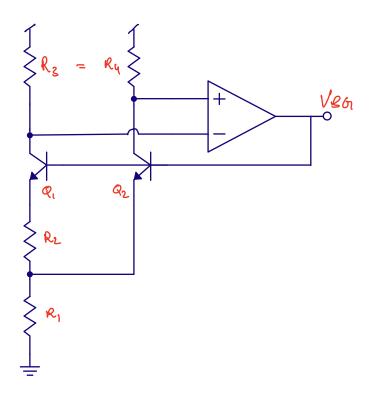

|   |            | 9.2.5   | Low voltage bandgap                          | 109      |

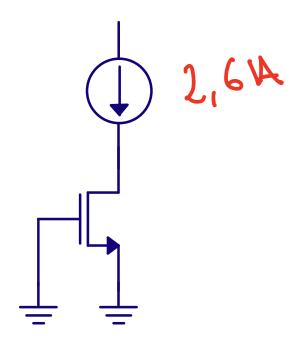

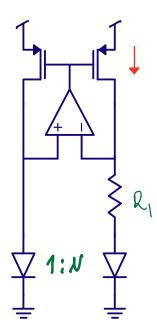

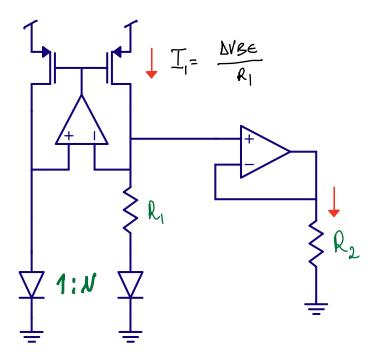

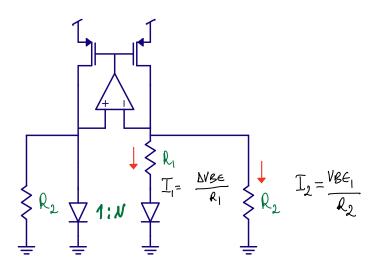

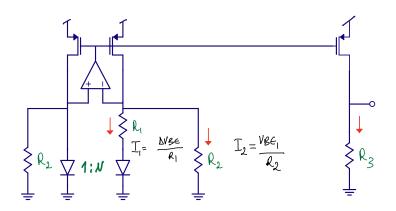

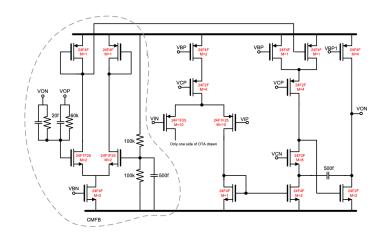

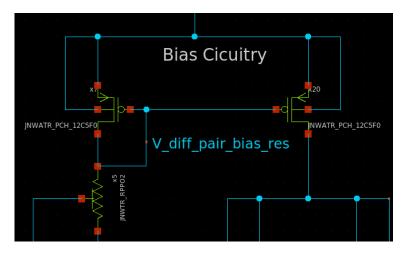

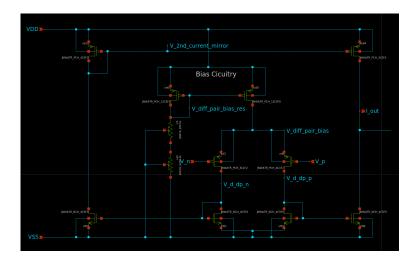

|   | 9.3        | Bias .  |                                              | 112      |

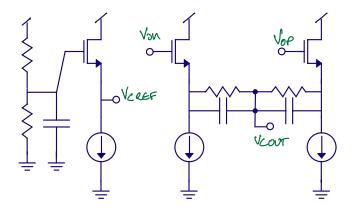

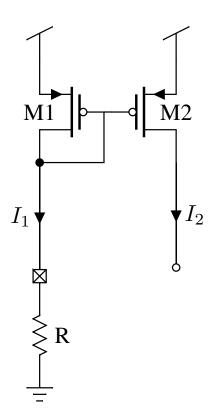

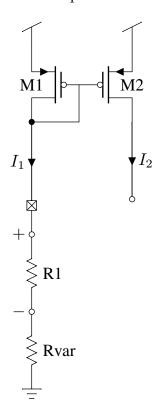

|   | -          | 9.3.1   | Voltage to current conversion                | 112      |

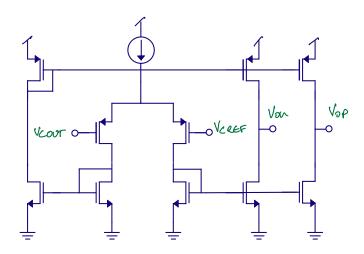

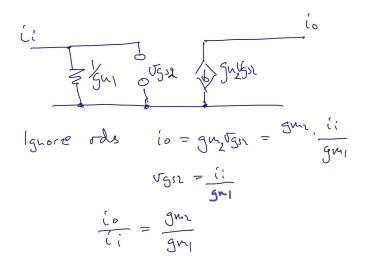

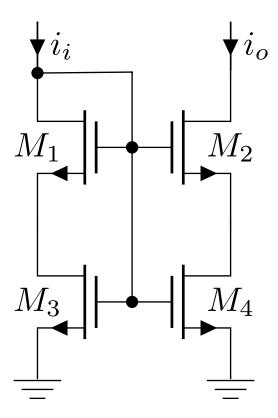

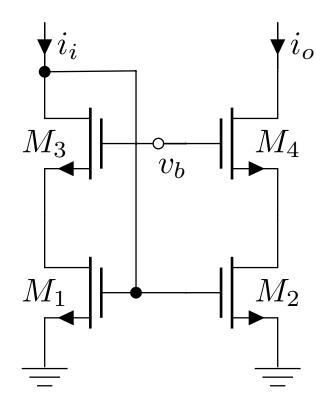

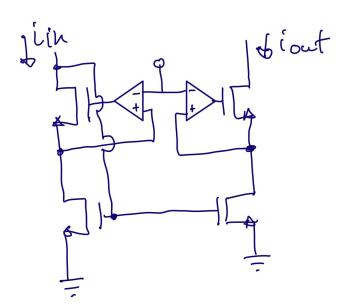

|   |            | 9.3.2   | GM Cell                                      | 113      |

|   | 9.4        |         | to learn more?                               | 115      |

| 10 | Ana  | log fron | ntend and filters                          | 117 |

|----|------|----------|--------------------------------------------|-----|

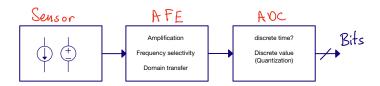

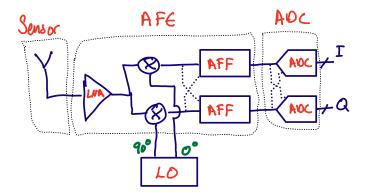

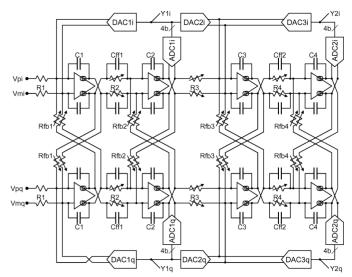

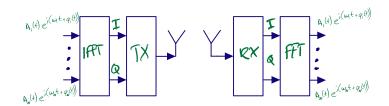

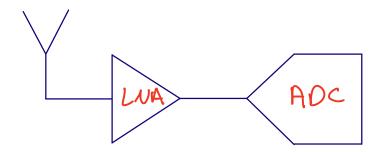

|    | 10.1 | Introd   | luction                                    | 117 |

|    | 10.2 | Filters  | 3                                          | 119 |

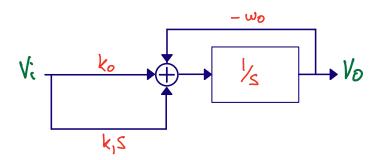

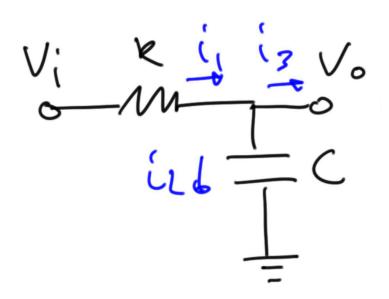

|    |      | 10.2.1   | First order filter                         | 120 |

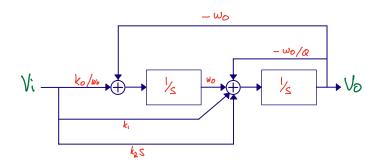

|    |      | 10.2.2   | Second order filter                        | 121 |

|    |      | 10.2.3   | How do we implement the filter sections?   | 122 |

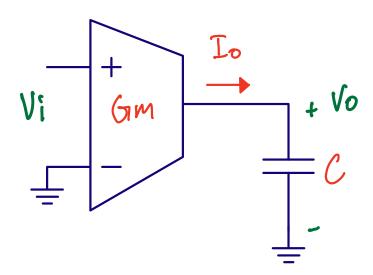

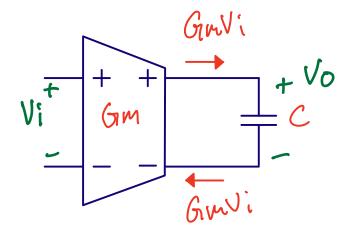

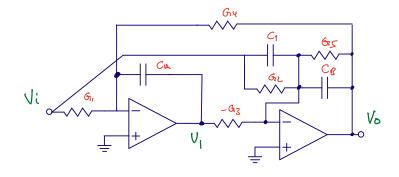

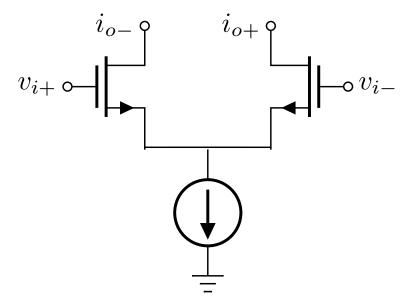

|    | 10.3 | Gm-C     | ,<br>, , , , , , , , , , , , , , , , , , , | 122 |

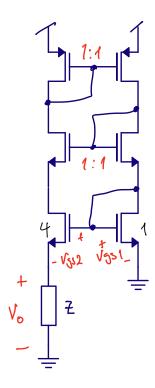

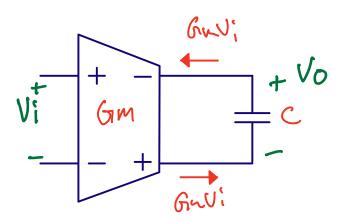

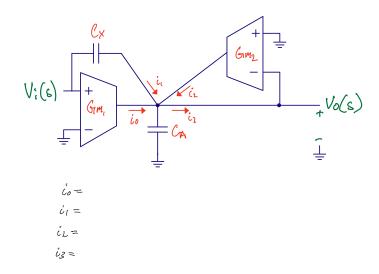

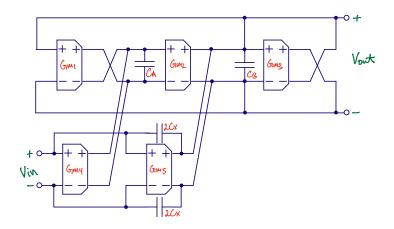

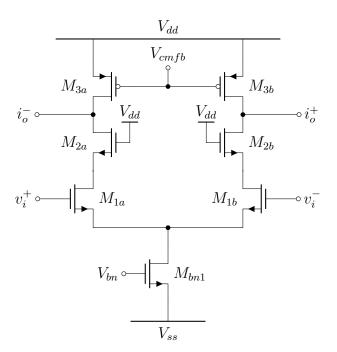

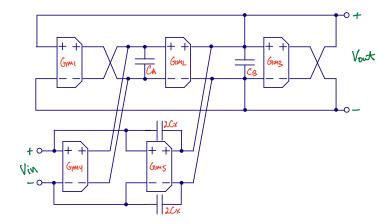

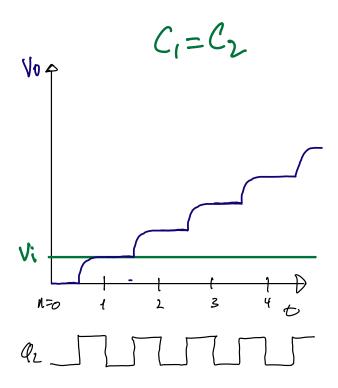

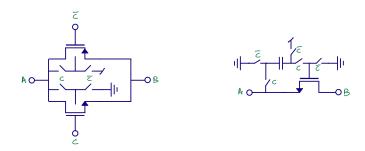

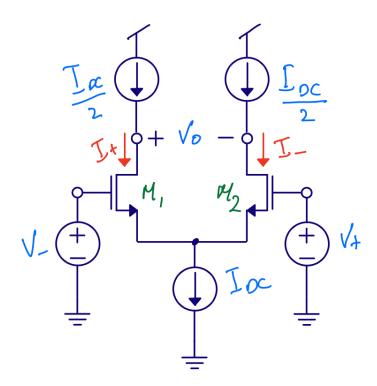

|    |      | 10.3.1   | Differential Gm-C                          | 123 |

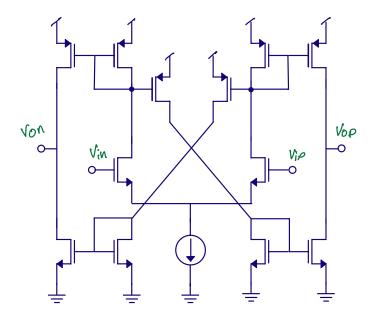

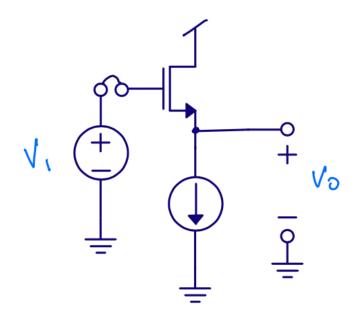

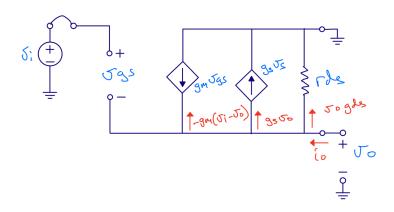

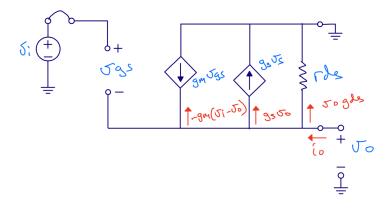

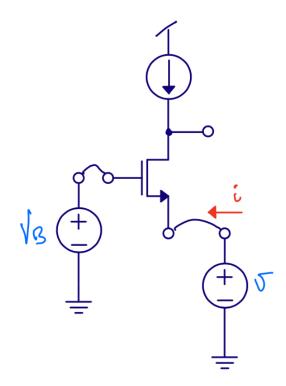

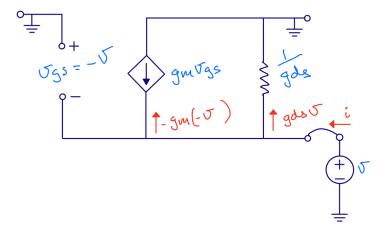

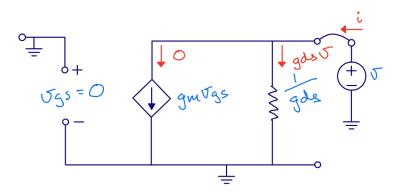

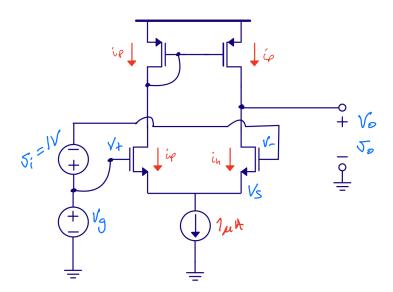

|    |      | 10.3.2   | Finding a transconductor                   | 125 |

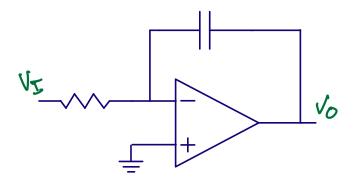

|    | 10.4 | Active   | e-RC                                       | 126 |

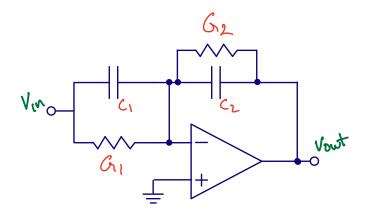

|    |      | 10.4.1   | General purpose first order filter         | 126 |

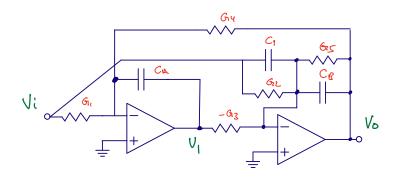

|    |      | 10.4.2   | General purpose biquad                     | 129 |

|    | 10.5 |          | OTA is not ideal                           | 130 |

|    | 10.6 | Exam     | ple circuit                                | 130 |

|    | 10.7 | -        | vorite OTA                                 | 131 |

|    | 10.8 | Want     | to learn more?                             | 133 |

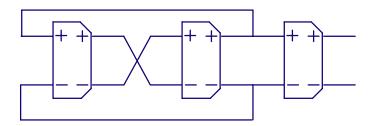

| 11 | Swi  |          | apacitor Circuits                          | 135 |

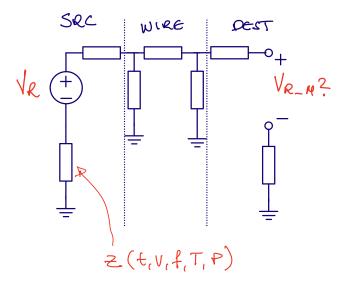

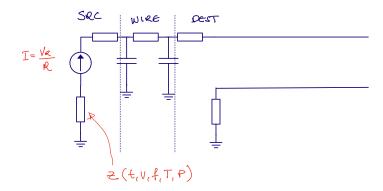

|    | 11.1 | Active   | e-RC                                       | 135 |

|    | 11.2 | Gm-C     |                                            | 137 |

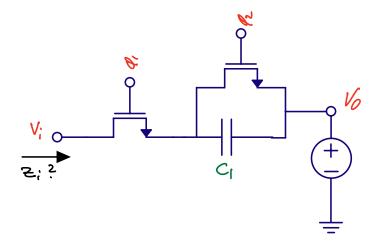

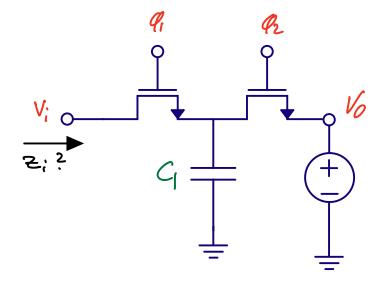

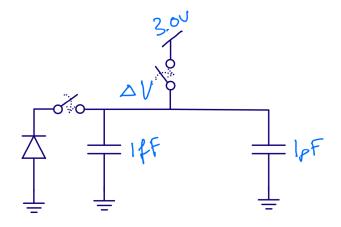

|    | 11.3 | Switcl   | hed capacitor                              | 137 |

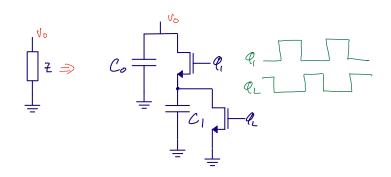

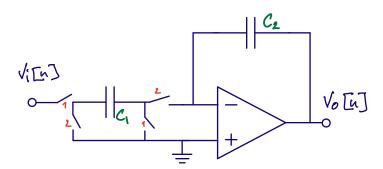

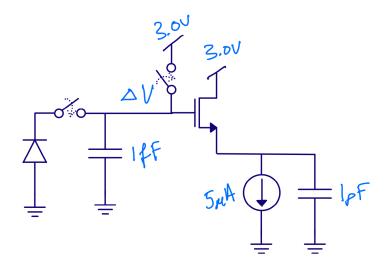

|    |      | 11.3.1   | An example SC circuit                      | 140 |

|    | 11.4 | Discre   | ete-Time Signals                           | 142 |

|    |      | 11.4.1   | The mathematics                            | 143 |

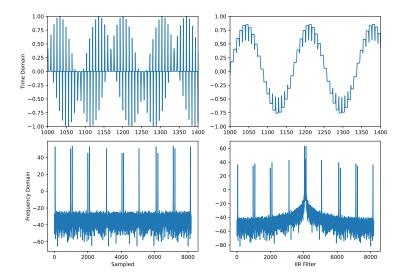

|    |      | 11.4.2   | Python discrete time example               | 144 |

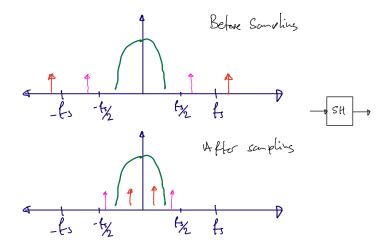

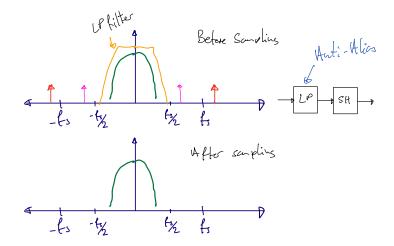

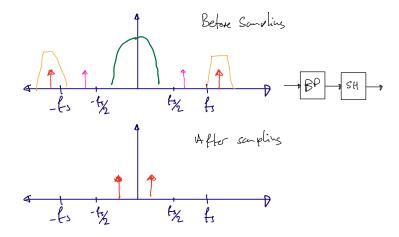

|    |      | 11.4.3   | Aliasing, bandwidth and sample rate theory | 145 |

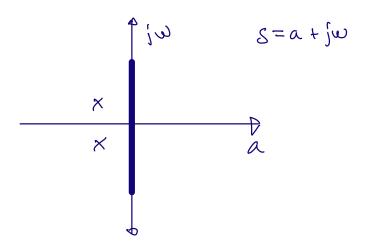

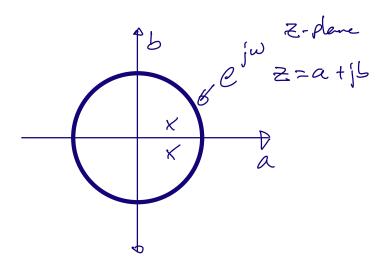

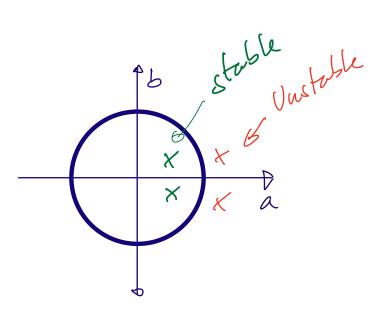

|    |      | 11.4.4   | Z-transform                                | 147 |

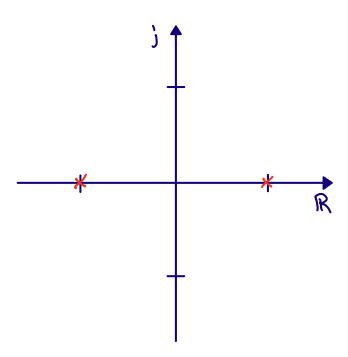

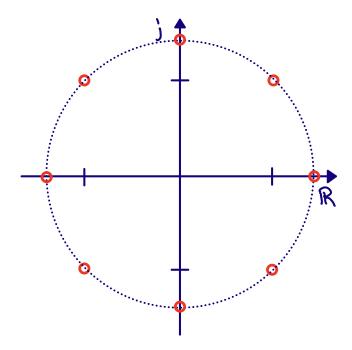

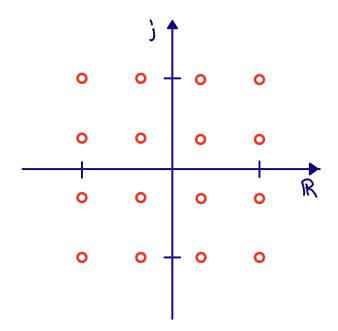

|    |      | 11.4.5   | Pole-Zero plots                            | 148 |

|    |      | 11.4.6   | Z-domain                                   | 148 |

|    |      | 11.4.7   | First order filter                         | 149 |

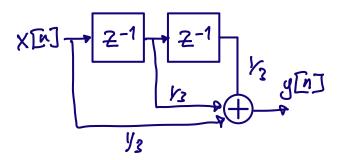

|    |      | 11.4.8   | Finite-impulse response(FIR)               | 151 |

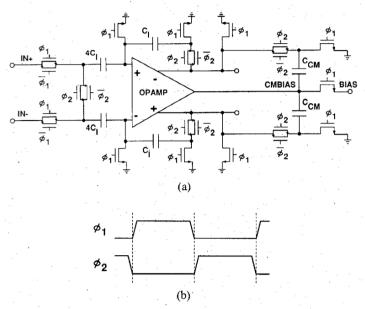

|    | 11.5 |          | hed-Capacitor                              | 152 |

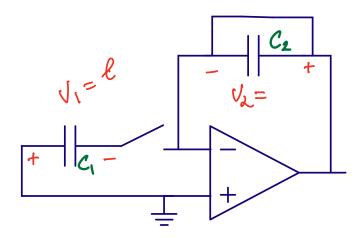

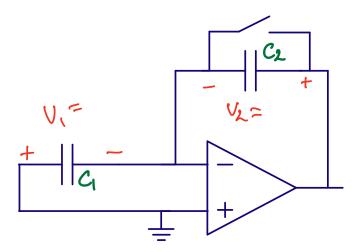

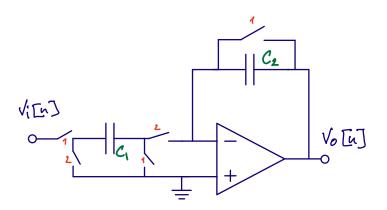

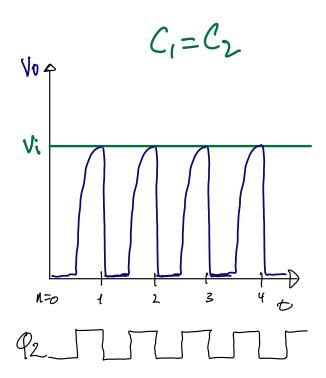

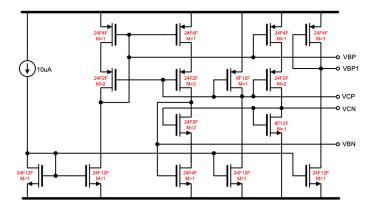

|    |      | 11.5.1   | Switched capacitor gain circuit            | 154 |

|    |      | 11.5.2   | Switched capacitor integrator              | 155 |

|    |      | 11.5.3   | Noise                                      | 156 |

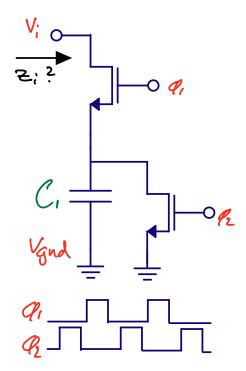

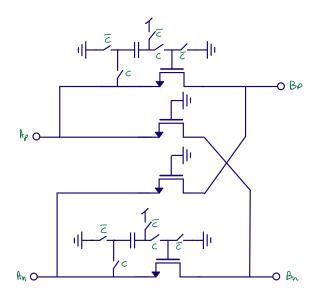

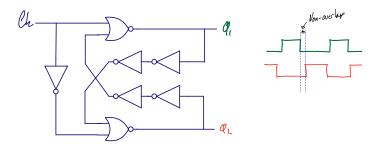

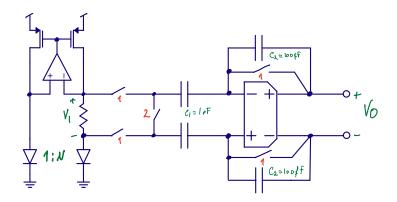

|    |      | 11.5.4   | Sub-circuits for SC-circuits               | 158 |

|    | 11 ( | 11.5.5   | Example                                    | 161 |

|    | 11.6 | Want     | to learn more?                             | 162 |

| 12 |      |          | ng and Sigma-Delta ADCs                    | 163 |

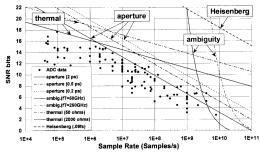

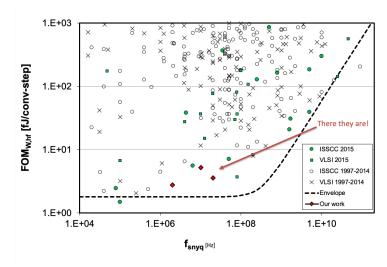

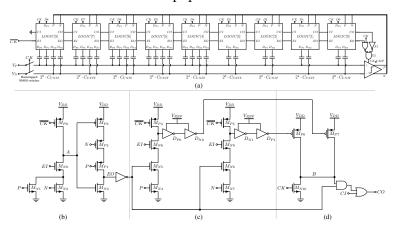

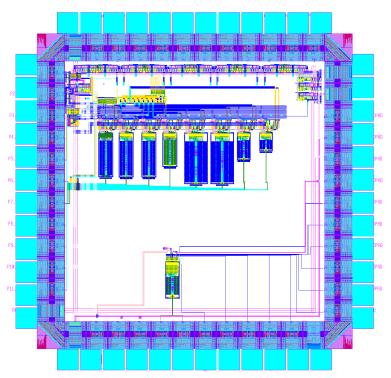

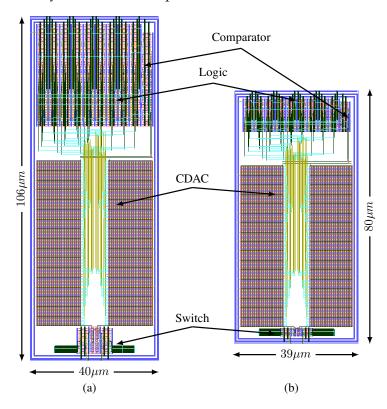

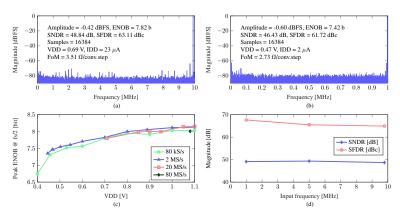

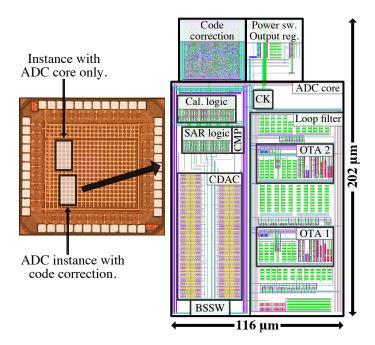

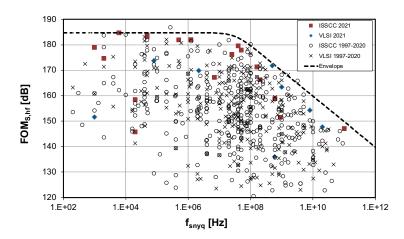

|    | 12.1 |          | state-of-the-art                           | 163 |

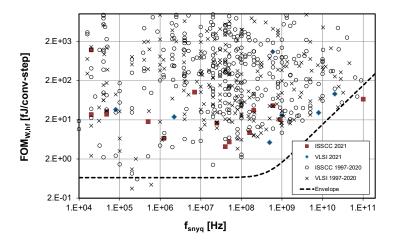

|    |      | 12.1.1   | What makes a state-of-the-art ADC          | 164 |

|    |      | 12.1.2   | High resolution FOM                        | 170 |

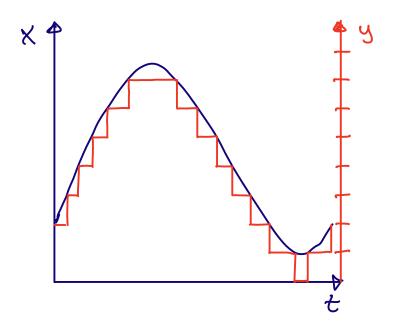

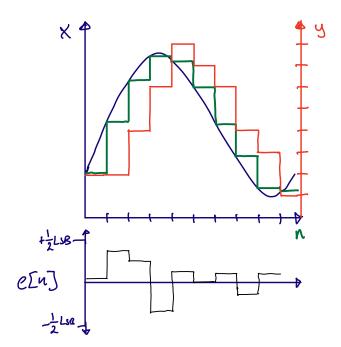

|    | 12.2 | -        | tization                                   | 171 |

|    |      | 12.2.1   | Signal to Quantization noise ratio         | 175 |

|    |      | 12.2.2   | 0 1                                        | 175 |

|    |      | 12.2.3   | Why you should care about quantization     | 4   |

|    | 46 - | 6        | noise                                      | 177 |

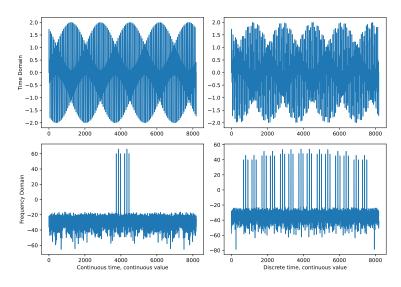

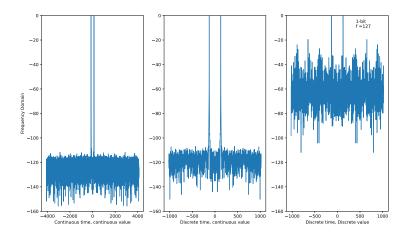

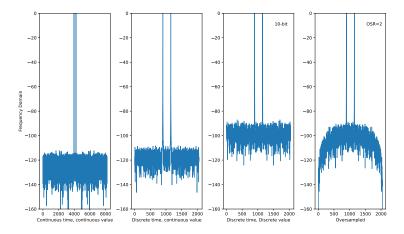

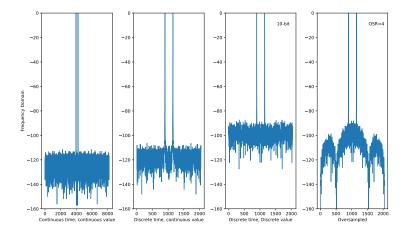

|    | 12.3 |          | ampling                                    | 178 |

|    |      | 12.3.1   | Noise power                                | 178 |

|    |      | 12.3.2   | Signal power                               | 179 |

|     |      | 12.3.3  | Signal to Noise Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 179 |

|-----|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |      | 12.3.4  | Signal to Quantization Noise Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 179 |

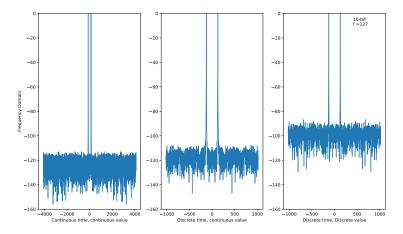

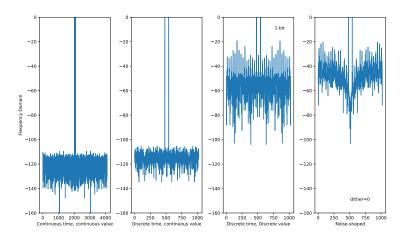

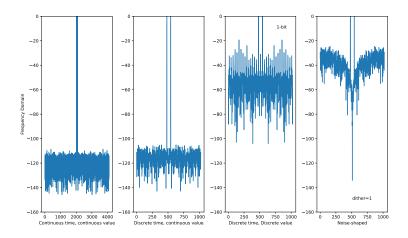

|     |      | 12.3.5  | Python oversample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 180 |

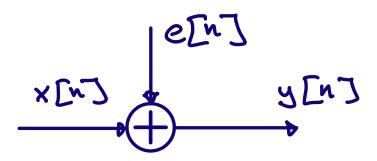

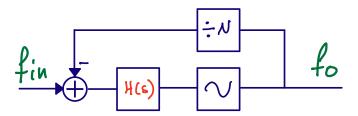

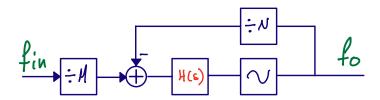

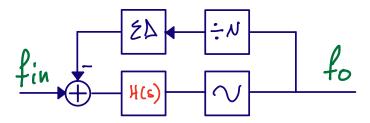

|     | 12.4 | Noise   | Shaping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 181 |

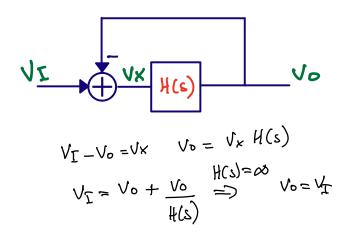

|     |      | 12.4.1  | The magic of feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 181 |

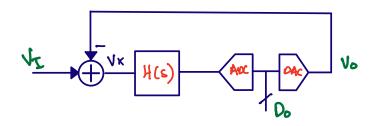

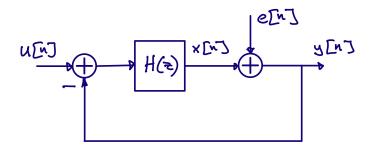

|     |      | 12.4.2  | Sigma-delta principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 182 |

|     |      | 12.4.3  | Signal transfer function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 184 |

|     |      | 12.4.4  | Noise transfer function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 184 |

|     |      | 12.4.5  | Combined transfer function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 185 |

|     | 12.5 | First-0 | Order Noise-Shaping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 185 |

|     |      | 12.5.1  | SQNR and ENOB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 187 |

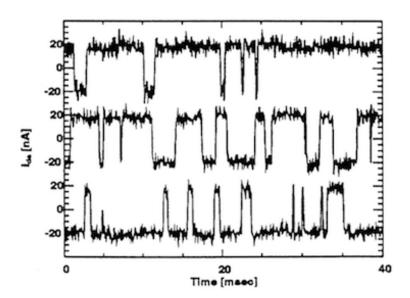

|     | 12.6 | Exam    | ples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 187 |

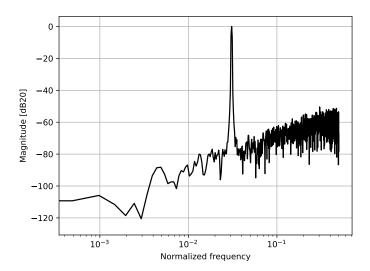

|     |      | 12.6.1  | Python noise-shaping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 187 |

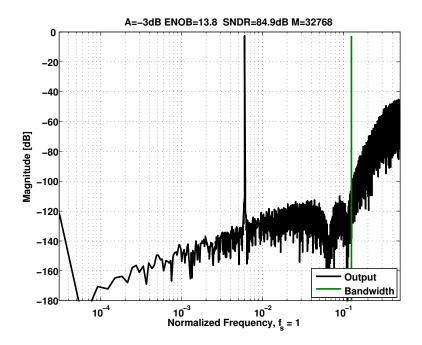

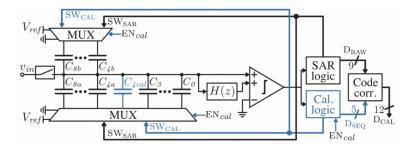

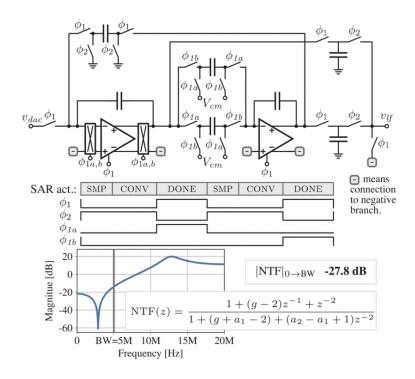

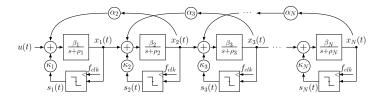

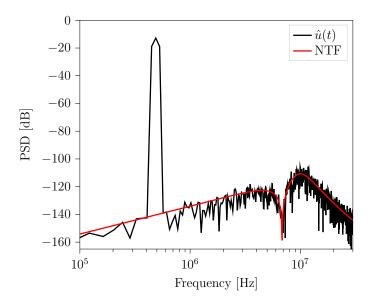

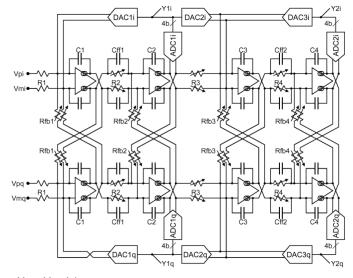

|     |      | 12.6.2  | The wonderful world of SD modulators .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 189 |

|     | 12.7 | Want    | to learn more?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 193 |

|     |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

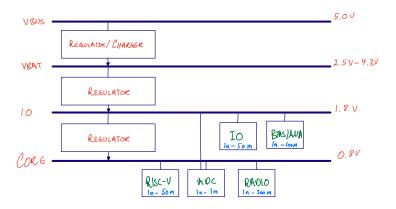

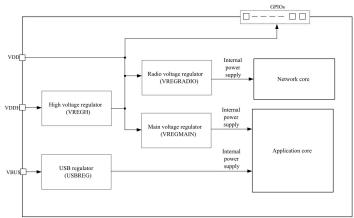

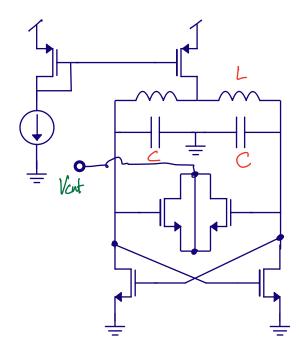

| 13  |      | age reg |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 195 |

|     | 13.1 | ,       | ge source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 195 |

|     |      | 13.1.1  | Core voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 199 |

|     |      | 13.1.2  | IO voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 199 |

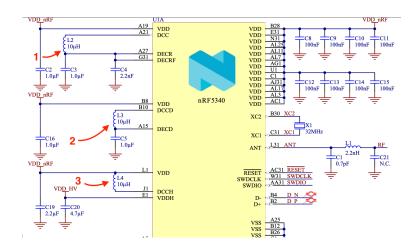

|     |      | 13.1.3  | Supply planning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 200 |

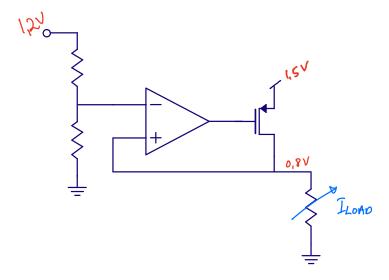

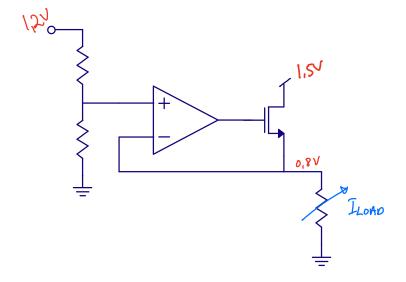

|     | 13.2 |         | r Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 201 |

|     |      | 13.2.1  | PMOS pass-fet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 201 |

|     |      | 13.2.2  | NMOS pass-fet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 202 |

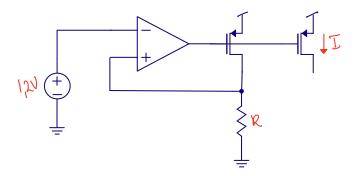

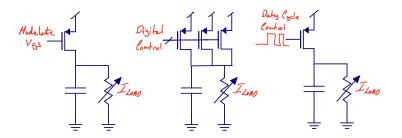

|     |      | 13.2.3  | Control of pass-fet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 203 |

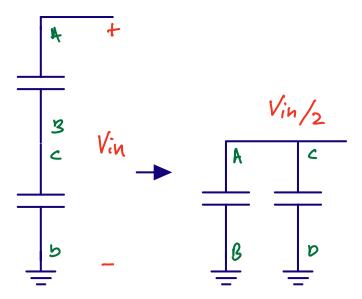

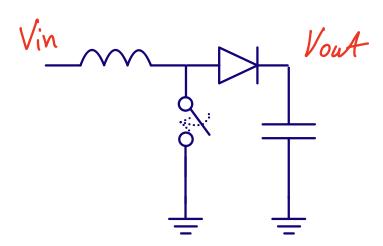

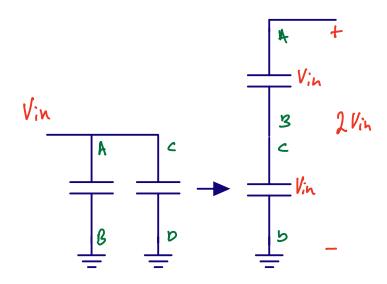

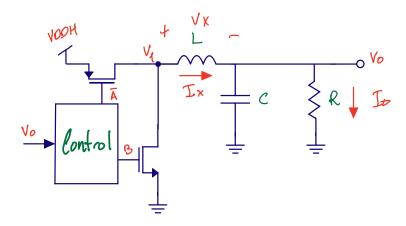

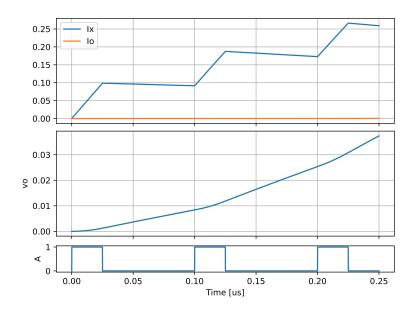

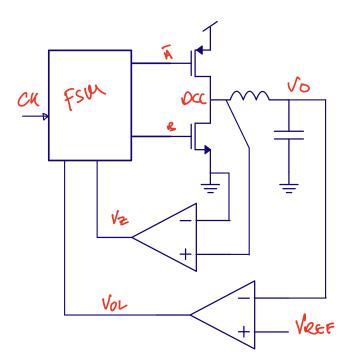

|     | 13.3 |         | hed Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 204 |

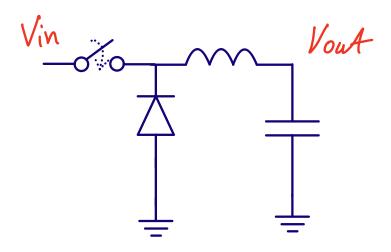

|     |      | 13.3.1  | Principles of switched regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 205 |

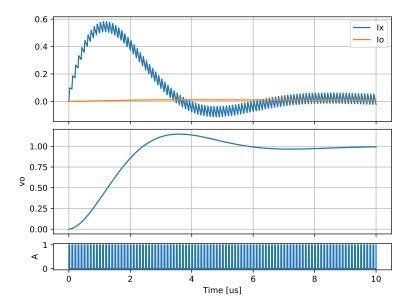

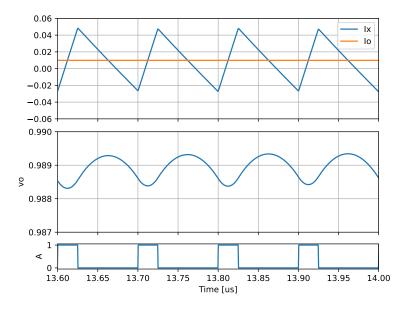

|     |      | 13.3.2  | Inductive DC/DC converter details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 208 |