## TFE4188 - Introduction to Lecture 2 ICs and ESD

#### Goal

Understand the real-world constraints on our IC

Understand why you must always handle ESD on an IC

Carsten Wulff 2023

2

The project for 2023 is to design an integrated temperature sensor. The hope is that some will tapeout on the Google/Efabless Open MPW shuttle

#### The real world constrains our IC

#### Q: What blocks must our IC include?

Carsten Wulff 2023

5

#### Electrostatic Discharge

If you make an IC, you must consider Electrostatic Discharge (ESD) Protection circuits

Standards for testing at JEDEC

#### When do ESD events occur?

Before/during PCB

After PCB

8

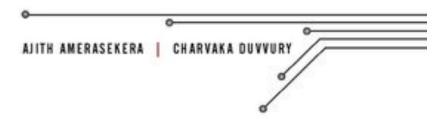

**Human body model (HBM)**

**Human body model (HBM)**

Charged device model (CDM)

System level ESD

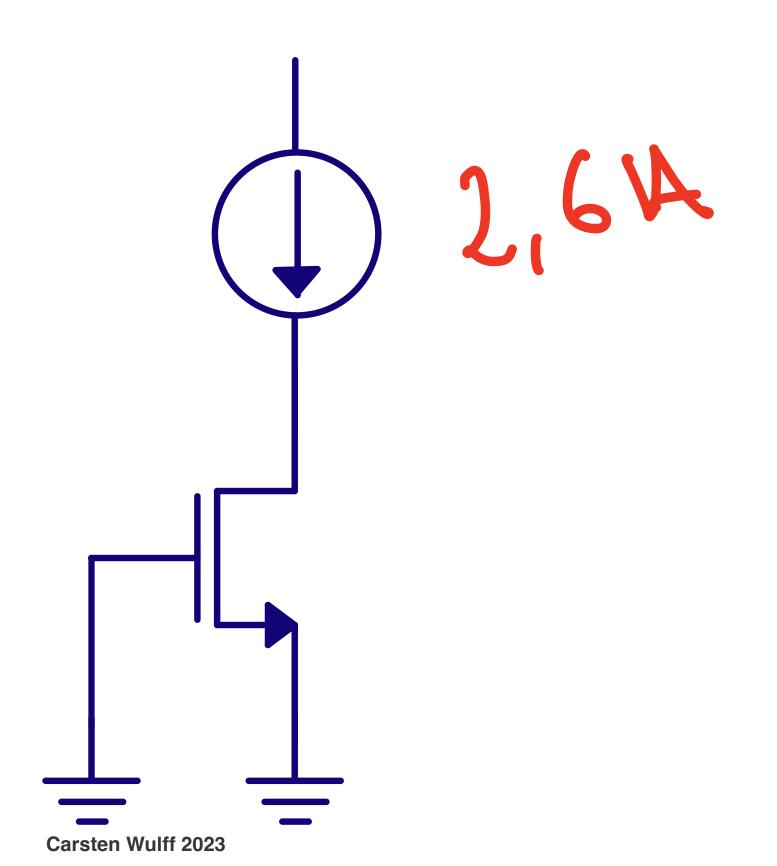

#### Human body model (HBM)

- Models a person touching a device with a finger

- Long duration (around 100 ns)

- Acts like a current source into a pin

- Can usually be handled in the I/O ring

- 4 kV HBM ESD is 2.67 A peak current

#### An ESD zap example

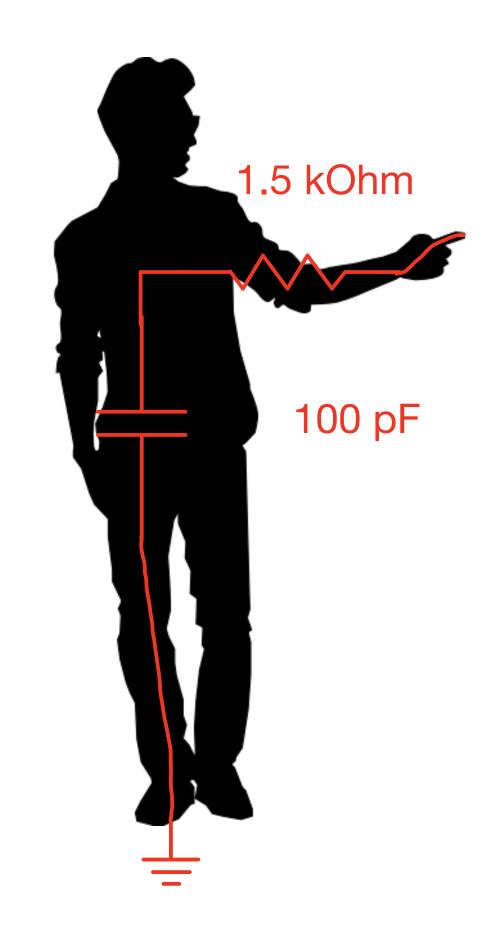

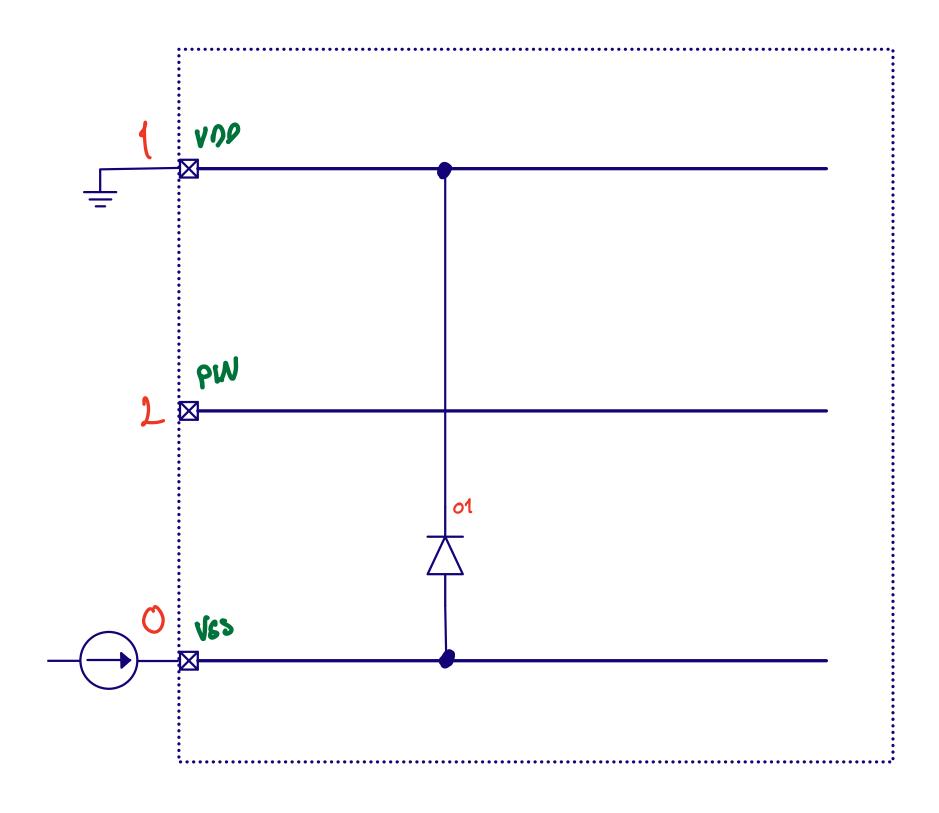

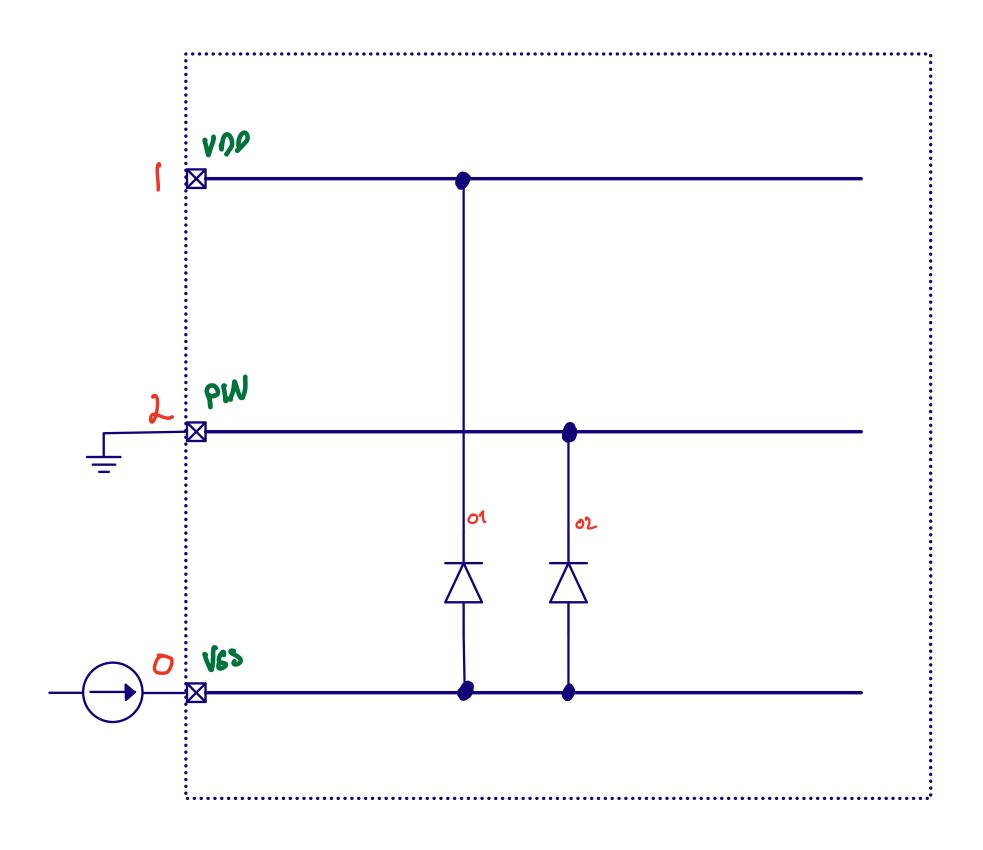

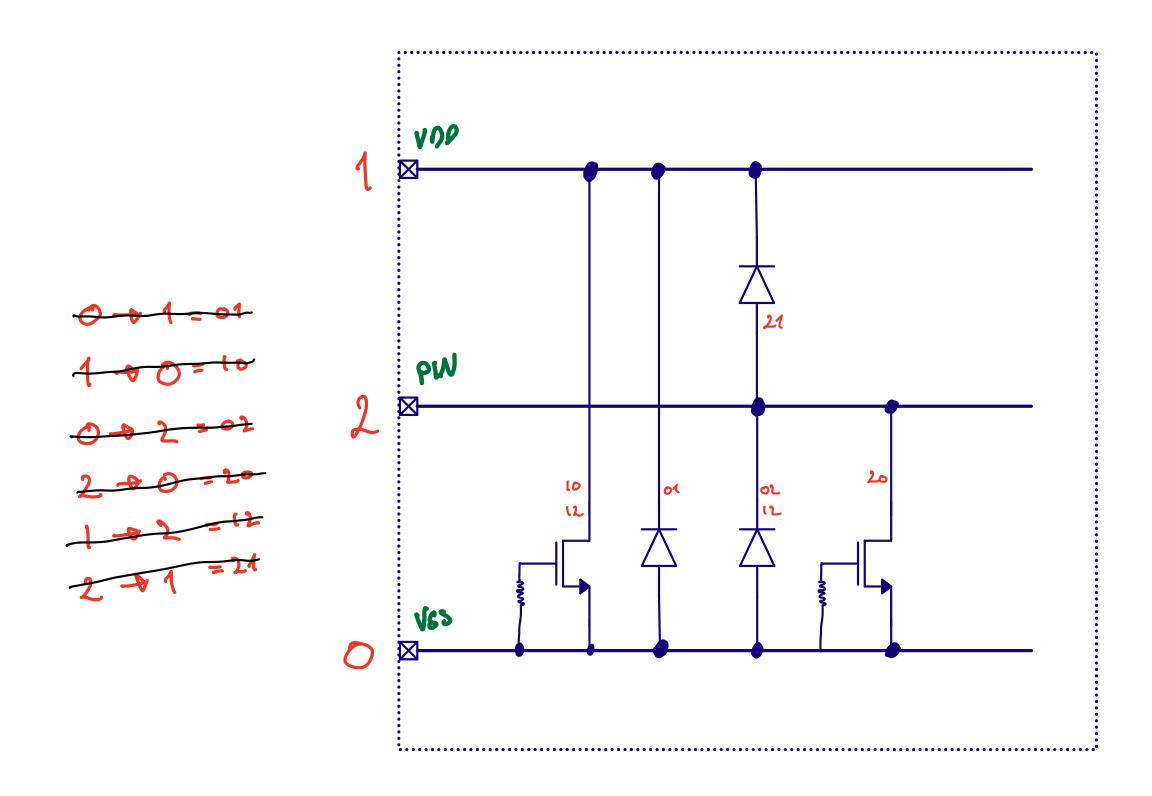

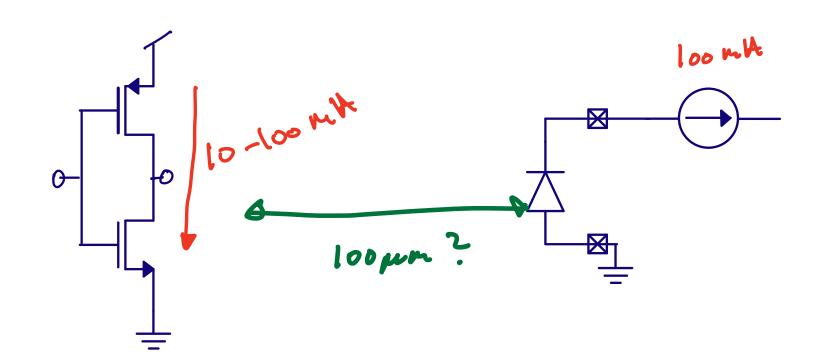

Imagine a ESD zap between VSS and VDD. How can we protect the device?

### Permutations 1 \* 0 \* VØD \* VØS 0 \* 2 \* VØS 2 \* 0 PN \* VØS 2 \* 0 PN \* VØS

## Q: Why does this work?

#### If you don't do the layout right<sup>3</sup>

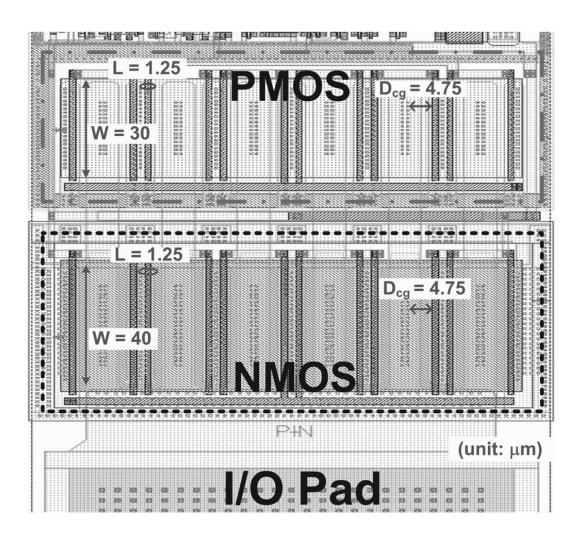

Fig. 5. Layout top view of the self-protecting fully silicided I/O buffer in a CMOS IC product.

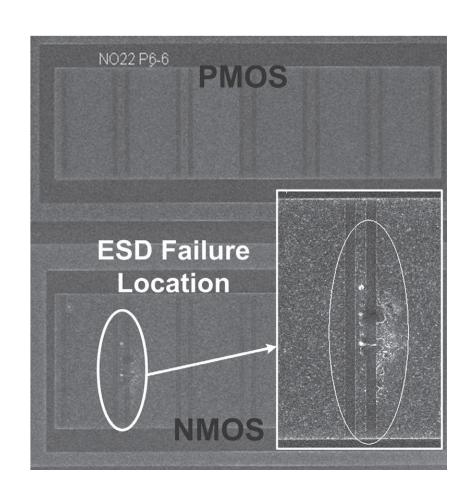

Fig. 6. SEM image of the fully silicided I/O buffer without ballasting after 2-kV PS-mode ESD stress. ESD failure is found on only one finger of the driver NMOS. Current filamentation is also observed on the surface of the driver NMOS without ballasting.

<sup>&</sup>lt;sup>3</sup>New Ballasting Layout Schemes to Improve ESD Robustness of I/O Buffers in Fully Silicided CMOS Process

Q: How can current in one place lead to a current somewhere else?

#### You must always handle ESD on an IC

- Do everything yourself

- Use libraries from foundry

- Get help www.sofics.com

# Thanks!